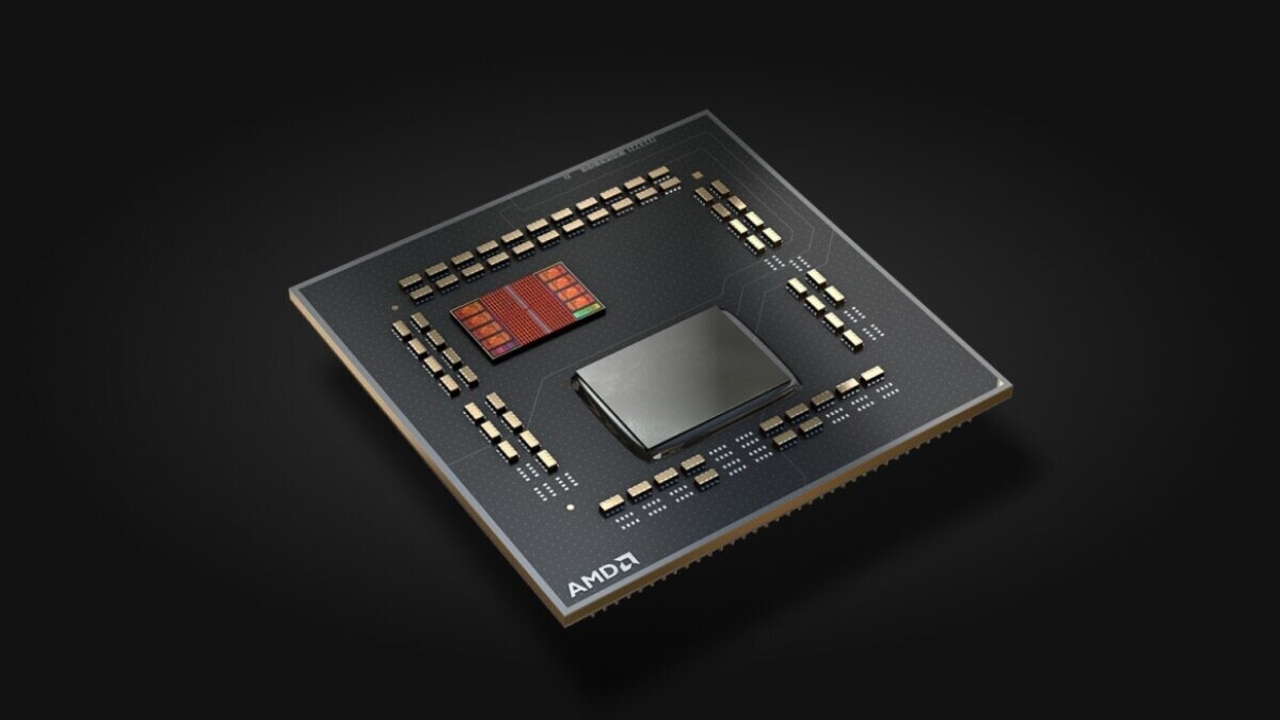

The latest leaked technical details regarding AMD’s next-generation processor architecture, Zen 6, prove that a major cache war has begun in the technology world. The company is pushing the 3D V-Cache technology, which directly impacts gaming performance, to even greater heights in this new generation. According to industry sources, Zen 6 processors with a single core die (CCD) are equipped with 144 MB of cache.

The 288 MB cache era begins

In high-end processors with dual core dies, this capacity doubles to 288 MB. These figures represent a massive capacity increase compared to AMD’s current Zen 5 “Granite Ridge” family. On the design side, AMD maintains its traditional structure, ensuring that each core die utilizes this massive cache pool with maximum efficiency.

This move by AMD is seen as a direct response to its biggest rival, Intel’s “Nova Lake” architecture. Intel, on its own front, plans to achieve similar capacities with its large end-level cache architecture, which it calls “bLLC”.

In terms of manufacturing technology, AMD utilizes TSMC’s most advanced nodes in its Zen 6 architecture. The core dies, which bear the brunt of the processor’s workload, are manufactured using TSMC’s 2nm N2P process. The I/O chip, which controls data input and output, uses the 3nm N3P manufacturing process. This hybrid manufacturing approach increases the energy efficiency of the processors and results in a significant jump in operating frequencies.